# Today's topic:

# Integrated devices and modeling (with focus on MOS transistor) (Chapter 1)

- A. Diode

- B. BJT

- C. MOSFET

- D. Resistor

- E. Capacitor

- F. SPICE modeling

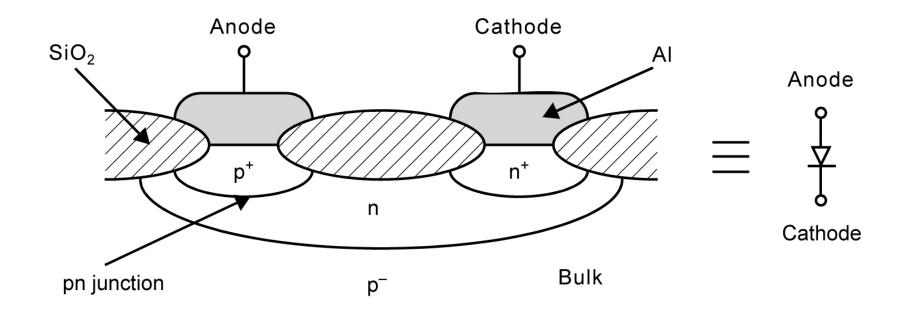

#### Cross section view of a Diode

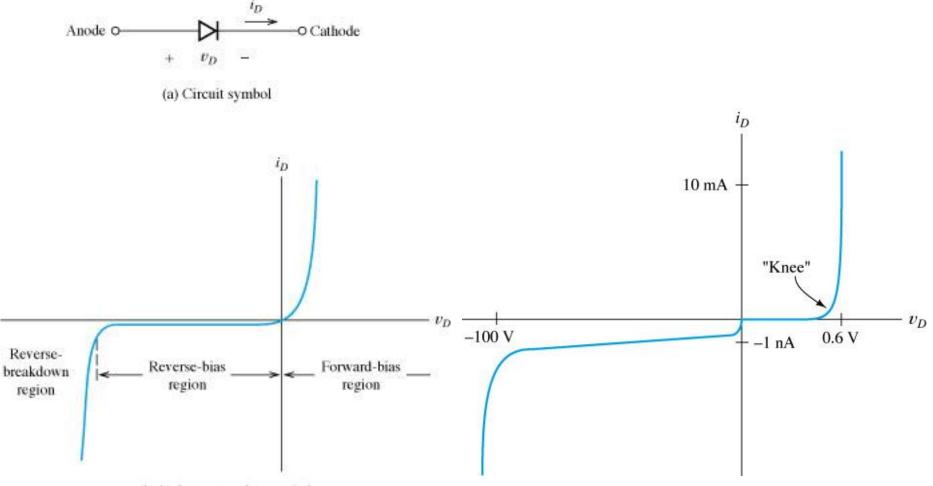

#### **Voltage-current relation of a Diode**

(b) Volt-ampere characteristic

# Linear small-signal equivalent circuit

• Many electronic circuits use DC supply voltages to bias a nonlinear device at an operating point and a small AC signal is injected into the circuit.

- In this case, analysis of the circuit can be split to two parts.

- First, DC analysis to find the operating point. In this part, nonlinear characteristics of the device must be considered.

- Second, AC (or small-signal) analysis is performed. In this part, the device characteristics are approximately linear if sufficiently small regions of operation is considered, a small linear small-signal equivalent circuit for the nonlinear device can be used for analysis.

- Small-signal linear equivalent circuit is a very important analysis approach that applies widely to electronic circuits.

# **Small-signal equivalent circuit of Diodes**

• In the case of diodes, DC supply voltage bias the diodes at the quiescent point, or called Q-point.

• At the Q-point, a small AC signal injected into the circuit swings the instantaneous point of operation slightly above and below the Q-point. For sufficiently small AC signal, the characteristics is straight.

We can define then

$$\Delta i_D = (di_D / dv_D)_Q \Delta v_D$$

$$r_d = [(di_D / dv_D)_Q]^{-1}$$

$$\Delta i_D \approx \Delta v_D / r_d$$

•Therefore, one can find the equivalent resistance of the diode from the small AC signal.

Figure 3.31 Diode characteristic illustrating the *Q*-point.

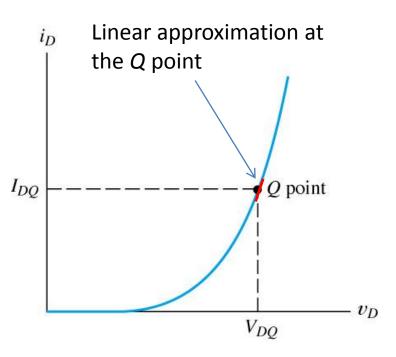

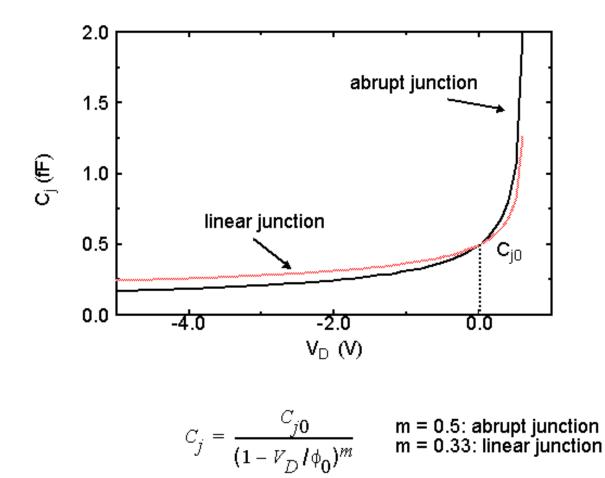

# **Depletion capacitance of diode**

Under reverse bias, the depletion region get wider with increasing voltage.

The charge in the depletion region is similar to the charge stored on a parallel-plate capacitor. However, additional charge increment in the depletion region is separated by a larger distance.

Thus the reverse bias junction behaves like a capacitor, but depletion region capacitance is not constant (or nonlinear).

Figure 3.47 As the reverse bias voltage becomes greater, the charge stored in the depletion region increases.

# **Depletion capacitance of diode II**

The depletion region capacitance is defined as

$$C_{j} = \frac{dQ}{dv_{D}}$$

$$C_{j} = \frac{C_{j0}}{[1 - V_{DQ} / \phi_{0j}]^{m}}$$

$$C_{j0} \text{ depletion cap acitance for zero bias voltage}$$

$$V_{DQ} \text{ operationg point voltage}$$

$$\phi_{0} \text{ built - in barrier potential} \quad \Phi_{0} = V_{T} \ln \left(\frac{N_{A}N_{D}}{n_{i}^{2}}\right)$$

$$m \text{ grading coefficien t}$$

$$c_{j0} = 2 pF$$

Figure 3.48 Depletion capacitance versus bias voltage for the 1N4148 diode.

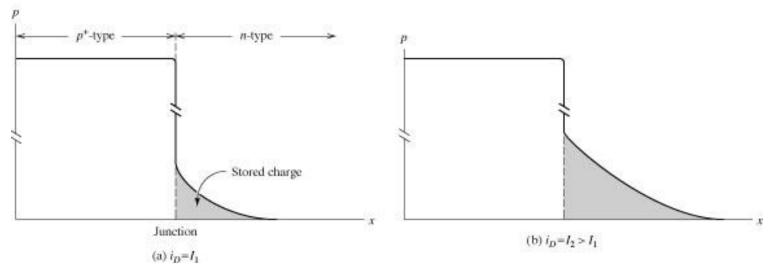

# **Diffusion capacitance of diode**

Another basic charge-storage mechanism occurs when the PN junction is forward biased.

For p<sup>+</sup>n junction (p type is more heavily doped) shown below, the current crossing the junction is mainly due to holes from the p-side to n-side. The charge associated with the holes that have crossed the junction is stored charge (represented in shaded area below). As current is increased, more holes cross the junction and stored charge increases.

This effect of charge storage is represented as diffusion capacitance.

$C_{dif} = \frac{\tau_T I_{DQ}}{V_T}, \tau_T \text{ average lifetime of minority carriers,}$  $I_{DQ} \text{ operatingpoint diode current,} V_T \text{ thermal voltage}$

Figure 3.49 Hole concentration versus distance for two values of forward current.

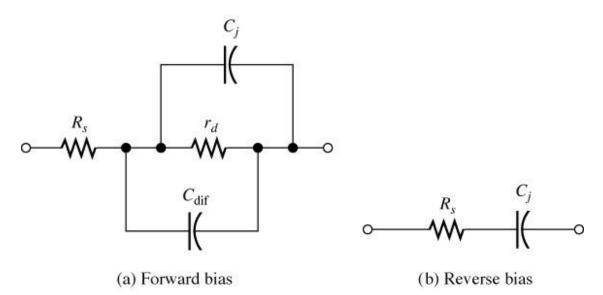

# Complete small-signal model of diode

- Complete small-signal model can be derived.

- Rs ohmic resistance of bulk material on both sides of the PN junction

- *r*<sup>*d*</sup> small-signal resistance of the diode

- C<sub>j</sub> depletion capacitance

- Cdif diffusion capacitance

- Under reverse bias, Cdif is 0 and rd is an open circuit.

- This small-signal equivalent circuit is valid for PN junction diode over a wide range of frequencies provided small-signal conditions apply.

Figure 3.50 Small-signal linear circuits for the *pn*-junction diode.

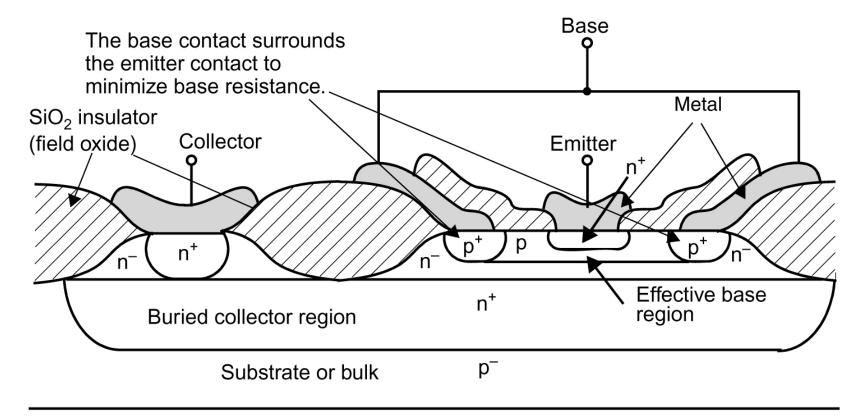

#### Cross section view of a BJT transistor

Chapter 8 Figure 01

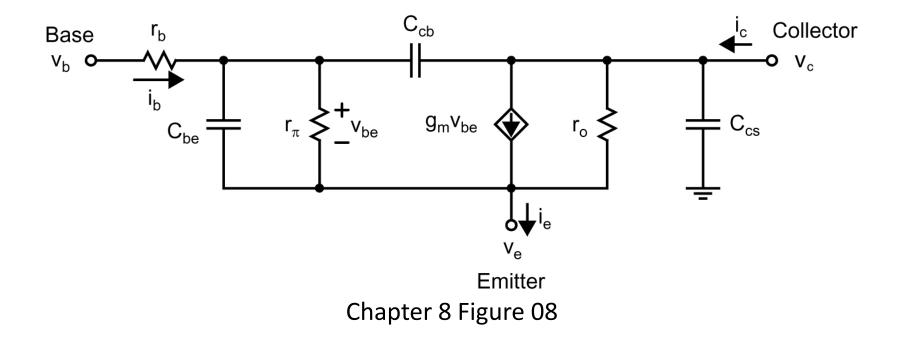

#### Small-signal model of a BJT transistor

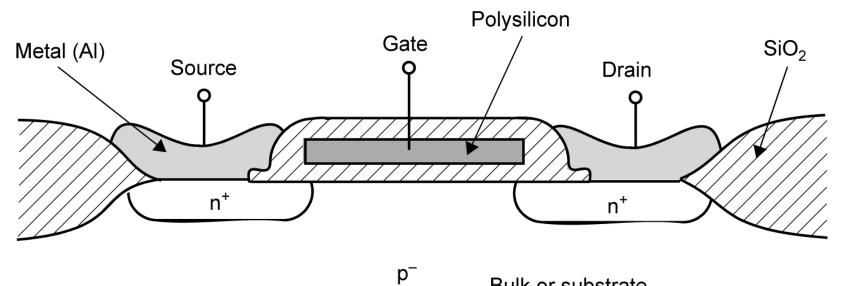

#### Cross section view of a MOS transistor

Bulk or substrate

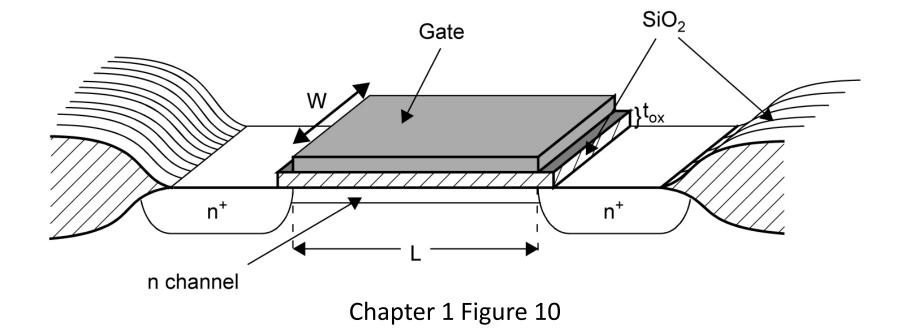

# The important dimension of a transistor

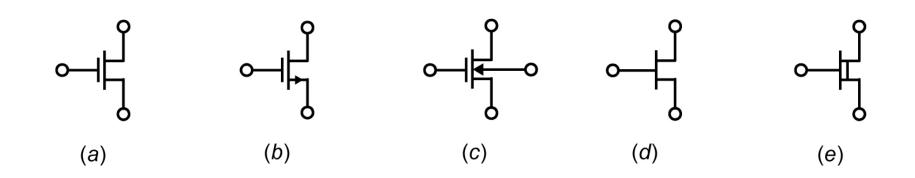

# MOS transistor symbols (NMOS)

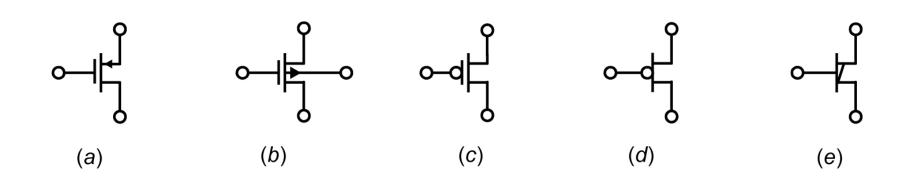

### MOS transistor symbols (PMOS)

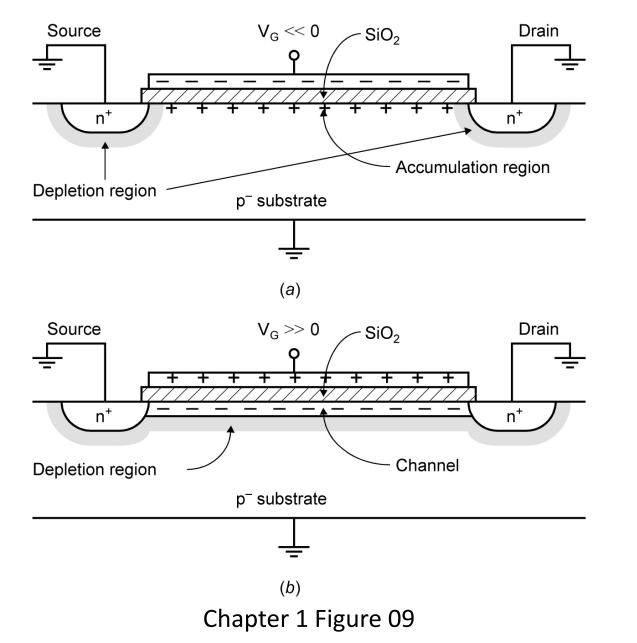

# **Transistor operation I**

# Resulting in an accumulated channel but no current flow

Resulting in an channel and current flow is possible depending on V<sub>DS</sub>

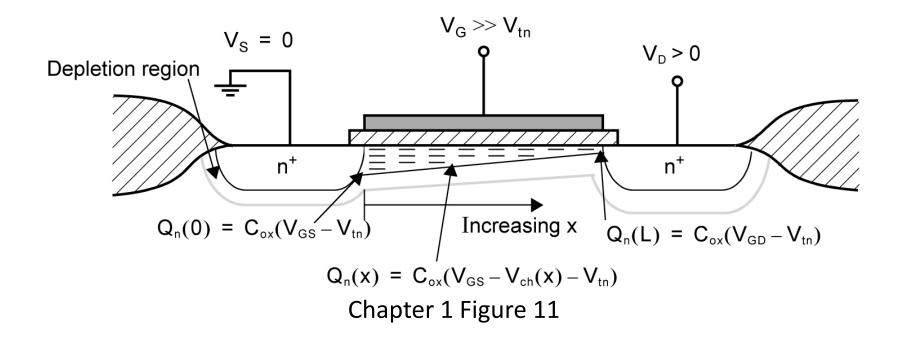

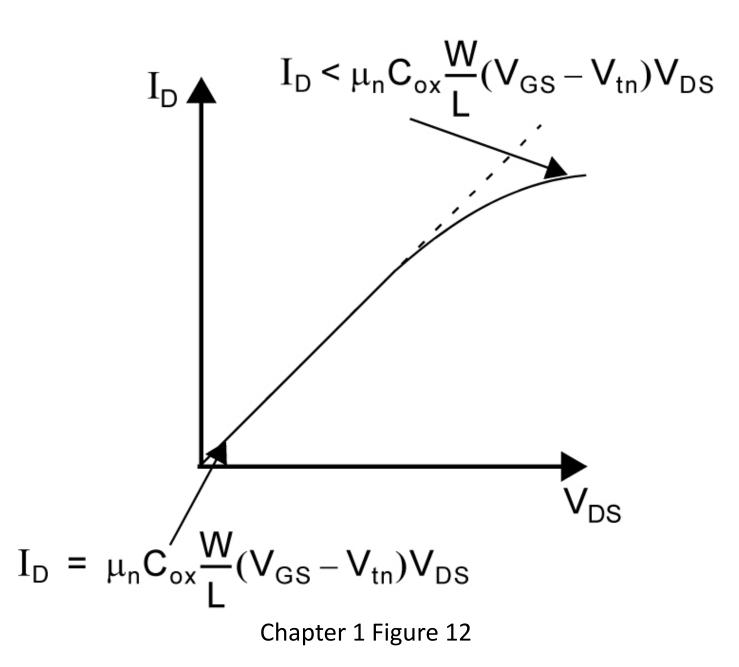

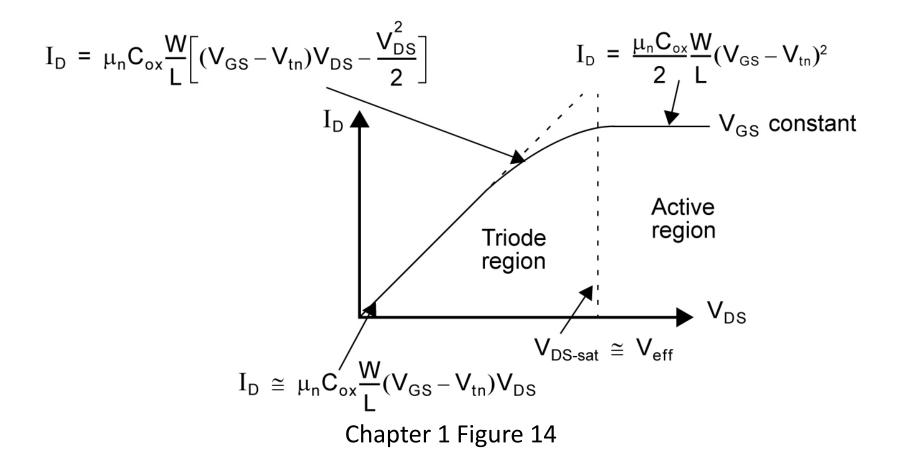

#### MOS operation II: triode(linear) region

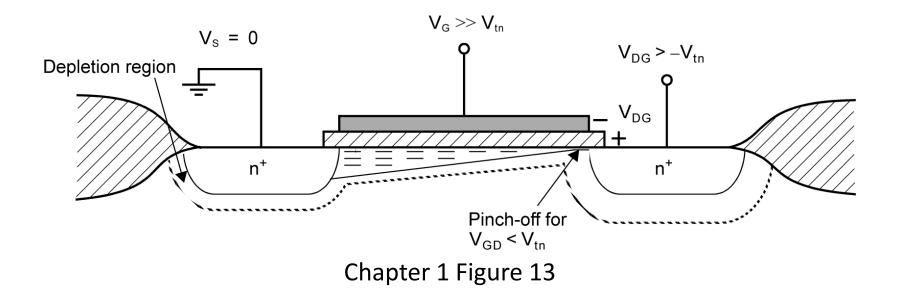

#### MOS operation III: saturation (active) region

## The threshold voltage

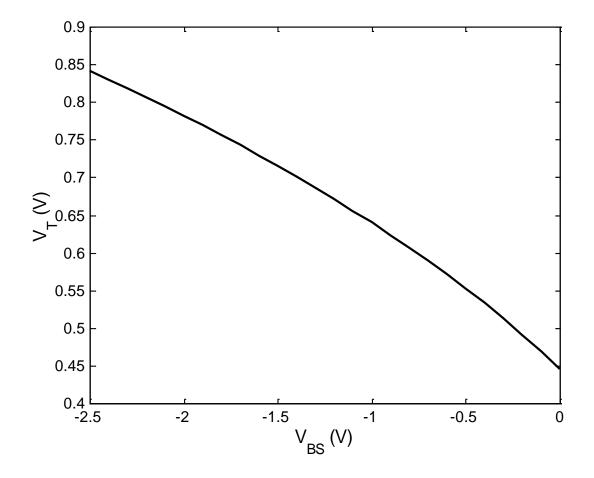

The threshold voltage of a transistor is not constant, but affected by the source-body voltage V<sub>SB</sub>, this is called body effect.

$$V_{tn} = V_{tn0} + \gamma(\sqrt{V_{SB} + |2\phi_F|} - \sqrt{|2\phi_F|})$$

where  $V_{tn0}$  is the threshold voltage with zero  $V_{SB}$  (source-to-body voltage),  $\phi_F = (kT/q) \ln(N_A/n_i)$  is the Fermi potential of the body, and

$$\gamma = \frac{\sqrt{2qN_AK_s\varepsilon_0}}{C_{ox}}$$

The factor  $\gamma$  is often called the *body-effect constant* and has units of  $\sqrt{V}$ . Notice that  $\gamma$  is proportional to  $\sqrt{N_A}$ ,<sup>12</sup> so the body effect is larger for transistors in a well where typically the doping is higher than the substrate of the microcircuit.

#### Body effect on threshold voltage: an example

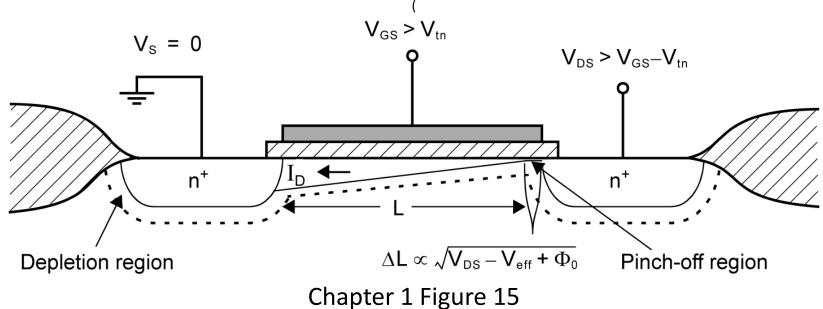

# **Channel length modulation**

$$\begin{split} I_{D} &= \frac{\mu_{n} C_{ox}}{2} \left(\frac{W}{L}\right) (V_{GS} - V_{tn})^{2} [1 + \lambda (V_{DS} - V_{eff})] \qquad V_{eff} = V_{GS} - V_{tn} \\ \lambda &= \frac{K_{ds}}{2L \sqrt{V_{DS} - V_{eff} + \phi_{0}}} \qquad \text{Note: inversely proportional to L} \\ k_{ds} &= \sqrt{\frac{2K_{s} \varepsilon_{0}}{qN_{A}}} \\ \Phi_{0} &= V_{T} \ln \left(\frac{N_{A} N_{D}}{n_{i}^{2}}\right) \qquad \text{Built in Junction potential} \end{split}$$

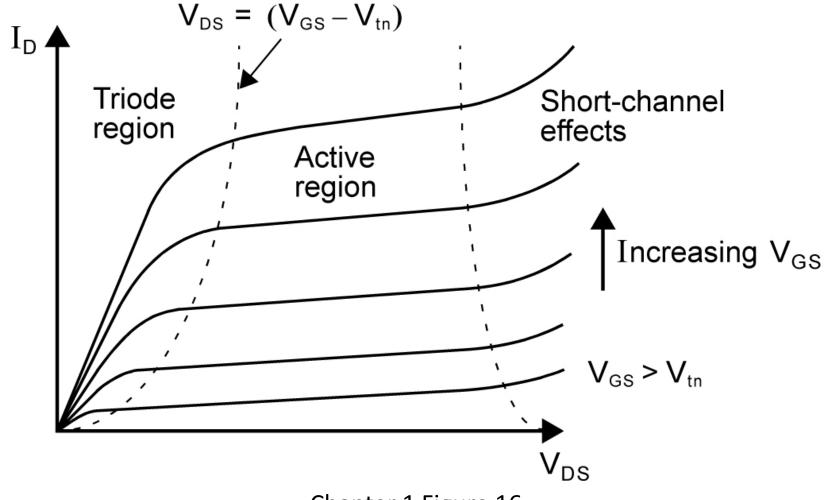

### A summary of operation regions

Chapter 1 Figure 16

In analog amplifiers, MOS transistors are mostly used in active regions, but in digital circuits they often operate in both regions.

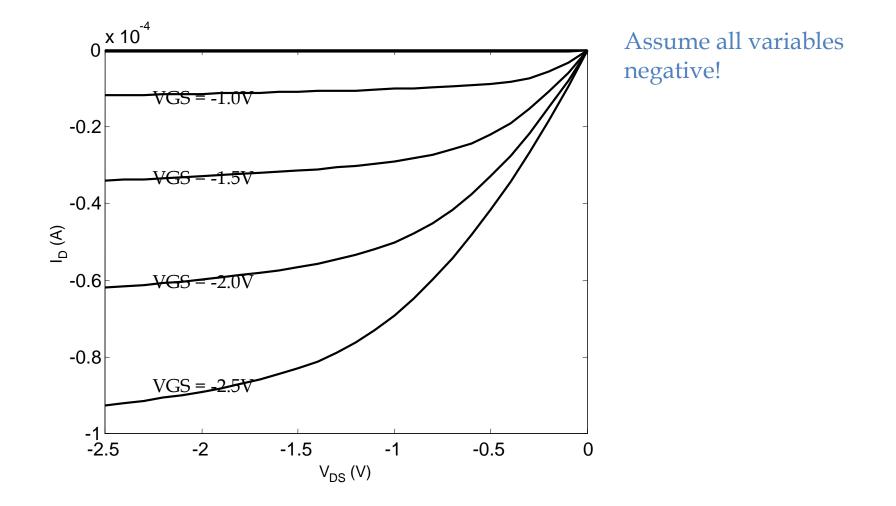

#### **Operation of a PMOS transistor**

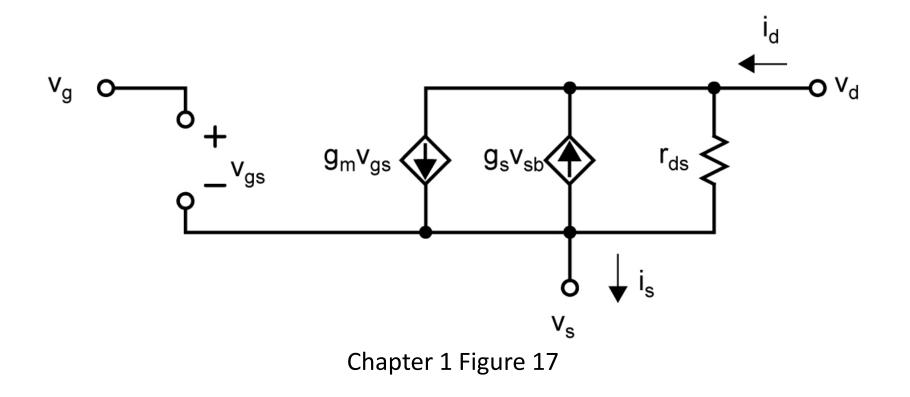

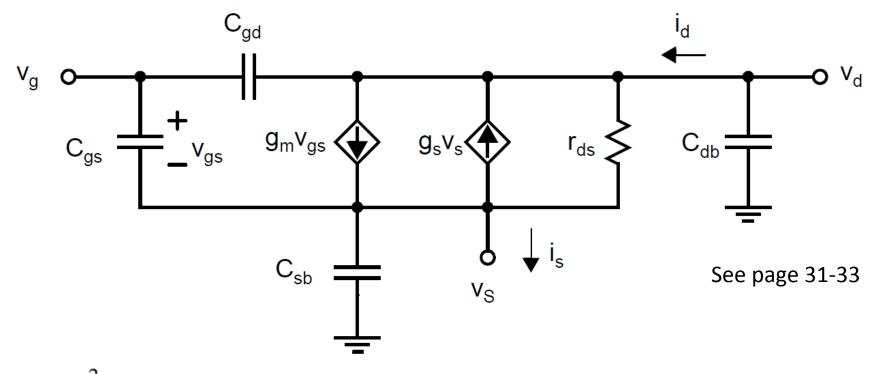

#### Low frequency small-signal model (active)

### Low frequency small-signal model (active)

$$\begin{split} g_m &= \frac{\partial I_D}{\partial V_{GS}} = \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{tn}) = \mu_n C_{ox} \frac{W}{L} V_{eff} \qquad V_{eff} \equiv V_{GS} - V_{tn} \\ g_m &= \sqrt{2\mu_n C_{ox} \frac{W}{L} I_D} \\ g_m &= \frac{2I_D}{V_{eff}} \end{split}$$

$$\frac{1}{r_{ds}} = g_{ds} = \frac{\partial I_{D}}{\partial V_{DS}} = \lambda \left(\frac{\mu_{n} C_{ox}}{2}\right) \left(\frac{W}{L}\right) (V_{GS} - V_{tn})^{2} = \lambda I_{D-sat} \cong \lambda I_{D} \qquad r_{ds} \cong \frac{1}{\lambda I_{D}}$$

See page 25-28

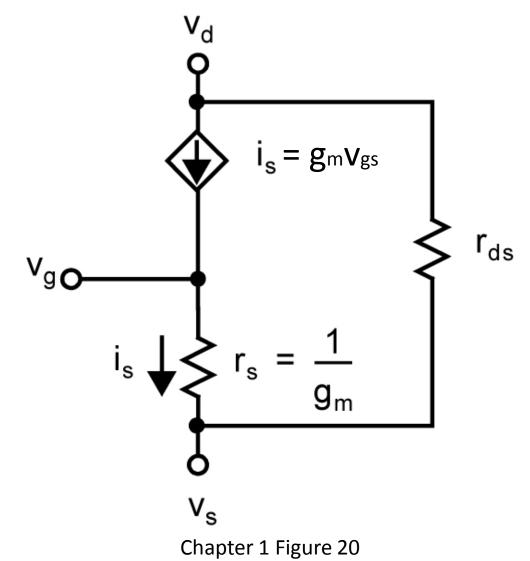

# <u>An alternative low frequency small-signal</u> <u>model</u>

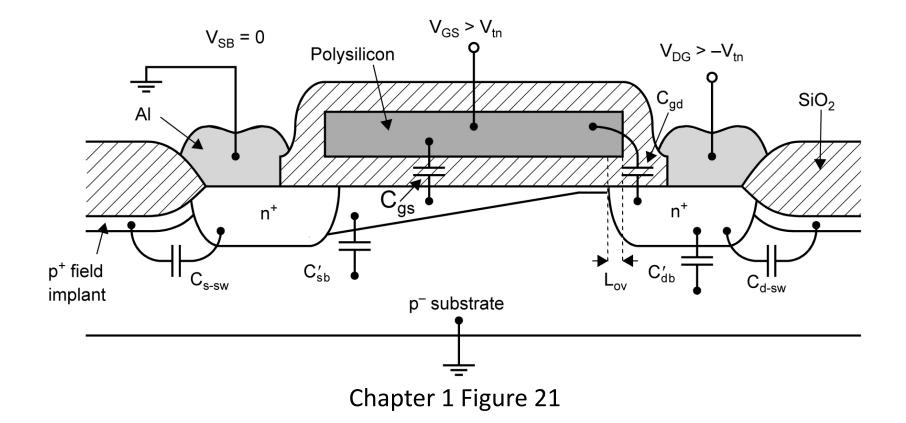

#### Understanding parasitic capacitance (active)

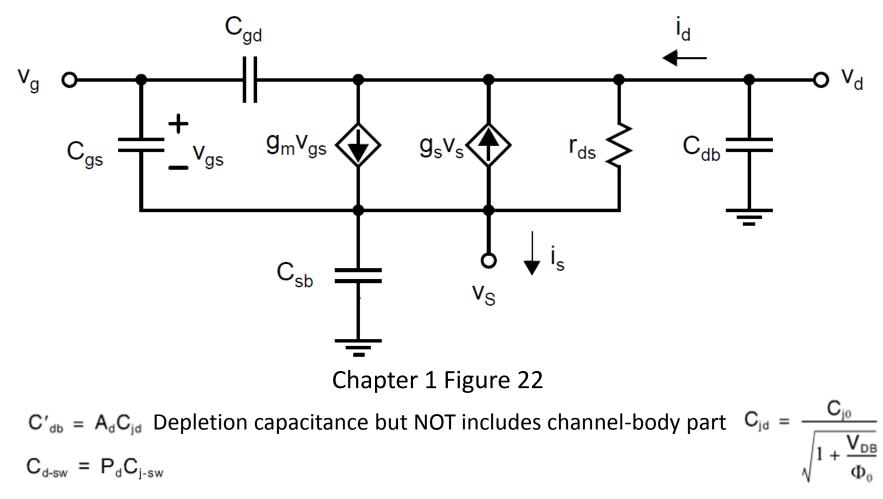

#### A little more detail on Cdb and Csb

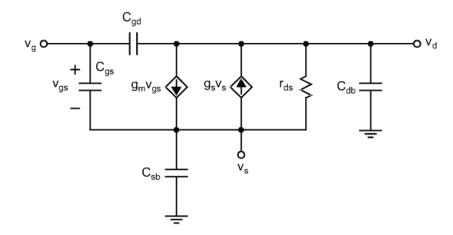

# High freqency small-signal model (active)

$C_{gs} = \frac{2}{3}WLC_{ox} + C_{ov}$  Due to the change in channel charge by Vgs voltage  $C'_{sb} = (A_s + A_{ch})C_{js}$  Depletion capacitance and includes channel-body part where A\_s is the area of the source junction, A\_{ch} is the area of the channel  $C_{js} = \frac{C_{j0}}{\sqrt{1 + \frac{V_{sB}}{\Phi_0}}}$

where  $P_s$  is the length of the perimeter of the source junction, excluding the side adjacent to the channel,

$$C_{sb} = C'_{sb} + C_{s-sw}$$

# High freqency small-signal model (active)

$C_{db} = C'_{db} + C_{d-sw}$

$C_{gd} = C_{ox}WL_{ov}$

See page 31-33

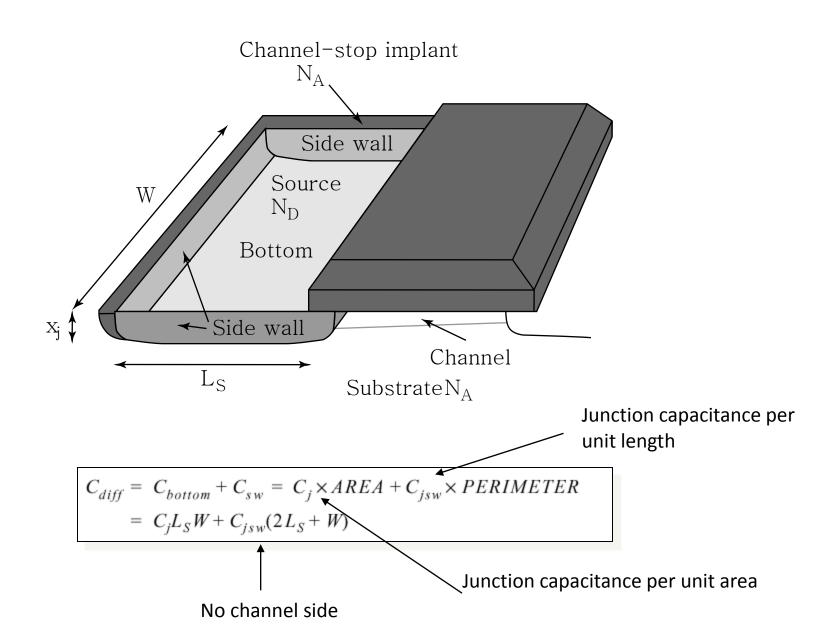

# **Junction Capacitance**

- Both C<sub>j</sub> and C<sub>jsw</sub> are non-linear and depends on the bias voltage.

- Keep large reverse-biased voltage for PN junction

# A note on drain-body and source-body PN junctions

• In MOS transistors, both drain-body and source-body PN junctions have to be reverse-biased at all times.

• This means that for NMOS transistors, drain-body and source-body voltage must be larger than 0. Therefore, for NMOS, the body terminal is typically connected to the lowest power supply (such as Gnd or Vss).

• For PMOS, then the body terminal should be connected to the highest power supply (such as Vdd).

#### Two examples

#### Example 1.13 on page 33

An n-channel transistor is modelled as having the following capacitance parameters:  $C_j = 2.4 \times 10^{-4} \text{ pF}/(\mu \text{m})^2$ ,  $C_{j-sw} = 2.0 \times 10^{-4} \text{ pF}/(\mu \text{m})$ ,  $C_{ox} = 1.9 \times 10^{-3} \text{ pF}/(\mu \text{m})^2$ ,  $C_{ov} = 2.0 \times 10^{-4} \text{ pF}/(\mu \text{m})$ . Find the capacitances  $C_{gs}$ ,  $C_{gd}$ ,  $C_{db}$ , and  $C_{sb}$  for a transistor having W = 100 µm and L = 2 µm. Assume the source and drain junctions extend 4 µm beyond the gate.

$$A_{s} = A_{d} = 400 (\mu m)^{2}$$

$$P_{s} = P_{d} = 108 \mu m$$

$$C_{gs} = \left(\frac{2}{3}\right) WLC_{ox} + C_{ov} \times W = 0.27 \text{ pF}$$

$$C_{gd} = C_{ov} \times W = 0.02 \text{ pF}$$

$$C_{sb} = C_{j}(A_{s} + WL) + (C_{j-sw} \times P_{s}) = 0.17 \text{ pF}$$

$$C_{db} = (C_{j} \times A_{d}) + (C_{j-sw} \times P_{d}) = 0.12 \text{ pF}$$

#### Two examples

Derive the complete small-signal model for an NMOS transistor with  $I_{DS}$ =100µA,  $V_{SB}$ =0.15V,  $V_{DS}$ =0.6V. Device parameters are  $2\phi_f = 0.65$ , W=10 $\mu$ m, L=0.18 $\mu$ m,  $\gamma$ = 0.4V<sup>1/2</sup>,  $\mu_n C_{ox}$  = 200 $\mu$ A / V<sup>2</sup>,  $\lambda$  = 0.4V<sup>-1</sup>,  $t_{ox} = 40$ Å = 4nm,  $\Psi_0 = 0.69$  V,  $C_{sb0} = C_{db0} = 9.3$ fF. Overlap capacitance from gate to source and gate to drain is 1fF. Assume  $C_{ab}$  =5fF.

$$g_{m} = \sqrt{2\mu_{n}C_{ox}\frac{W}{L}I_{D}} = \sqrt{2\times200\times10^{-6}\times\frac{10}{0.18}\times100\times10^{-6}} \frac{A_{V}}{V} = 1.5 \frac{mA_{V}}{V}$$

With V<sub>SB</sub>=0.15V, we find

$$C_{sb} = \frac{C_{sb0}}{\left(1 + \frac{V_{SB}}{\psi_0}\right)^{1/2}} = \frac{9.3}{\left(1 + \frac{0.15}{0.69}\right)^{1/2}} fF = 8.4 fF$$

Hence,

$$C_{db} = \frac{C_{db0}}{\left(1 + \frac{V_{DB}}{\psi_0}\right)^{1/2}} = \frac{9.3}{\left(1 + \frac{0.75}{0.69}\right)^{1/2}} fF = 6.4 fF$$

The oxide capacitance per unit area is

$$C_{ox} = \frac{\varepsilon_r \varepsilon_{SiO_2}}{t_{ox}} = \frac{3.9 \times 8.854 \times 10^{-14} \, F/cm}{40 \times 10^{-10} \, m} \sim 8.6 \, \frac{fF}{(\mu m)^2}$$

The intrinsic portion of the gate source capacitance is

$$C_{gs} = \frac{2}{3} \times 10 \times 0.18 \times 8.6 \, fF \sim 10 \, fF$$

$g_{mb} = \gamma \sqrt{\frac{\mu_n C_{ox} \frac{W}{L} I_D}{2(2\phi_s + V_{ox})}} = 0.4 \sqrt{\frac{200 \times 10^{-6} \times \frac{10}{0.18} \times 100 \times 10^{-6}}{2 \times (0.65 \pm 0.15)}} \frac{A_V}{V} = 333 \frac{\mu A_V}{V}}$  The voltage from drain to body is  $V_{DB} = V_{DS} + V_{SB} = 0.75V$  $r_o = \frac{1}{\lambda I_o} = \frac{1}{0.4 \times 100 \times 10^{-6}} = 25k\Omega$

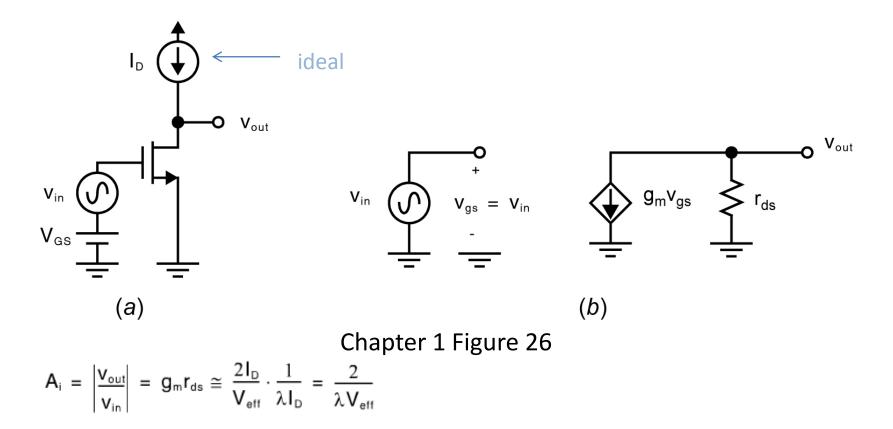

# Analog Figure-of-Merit

With so many small-signal parameters, it is useful to have a single number that captures key aspects of transistor performance.

Two such figure of merits are intrinsic gain (low frequency performance) and intrinsic speed (high frequency performance).

#### Analog Figure-of-Merit I

Two important general conclusions on analog design:

- 1. To maximize DC or low frequency gain, transistor needs to have small Veff

- 2. Intrinsic gain is maximized when gate length L is large so that  $\lambda$  is small

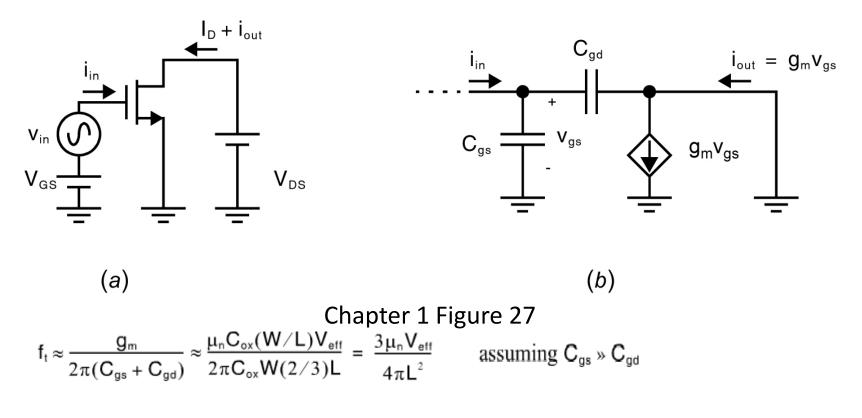

## Analog Figure-of-Merit II

The unit-gain frequency of a transistor, ft, is to provide a measure of the maximum operating frequency at which a transistor is useful (used as a measure of intrinsic speed).

The UGF is defined as the maximum frequency at which the amplitude of the output small-signal current |lout| is still larger than |lin|.

# Analog Figure-of-Merit II

As with intrinsic gain, some important fundamental conclusions about analog design can be drawn:

- 1. For operation at high-speed, devices parasitic capacitances should be minimized, which implies minimizing device gate length L.

- 2. Speed is maximized by biasing with high values of Veff.

Note that there requirements are in direct conflict with those for maximum gain.

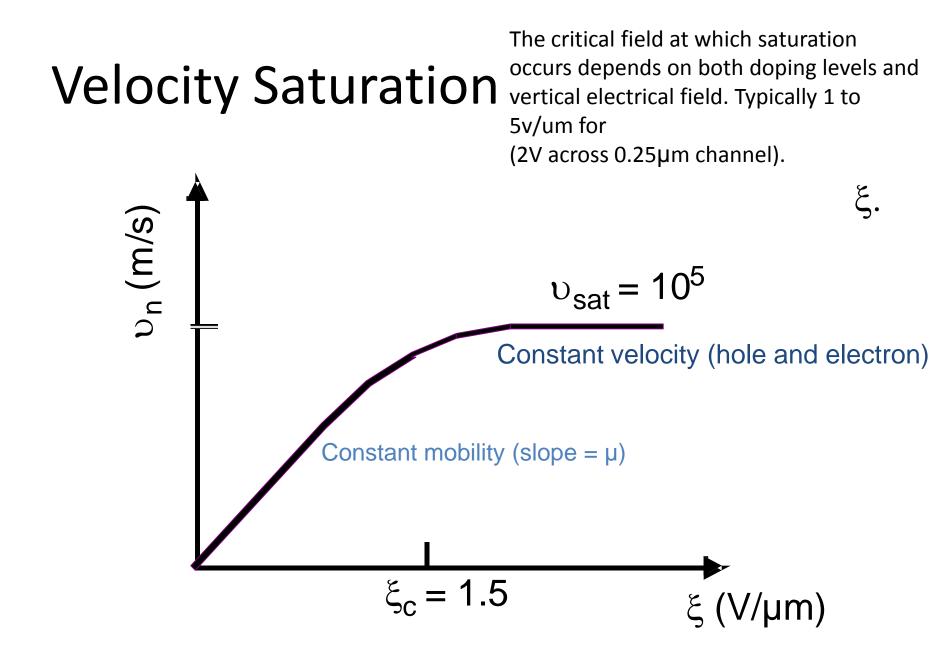

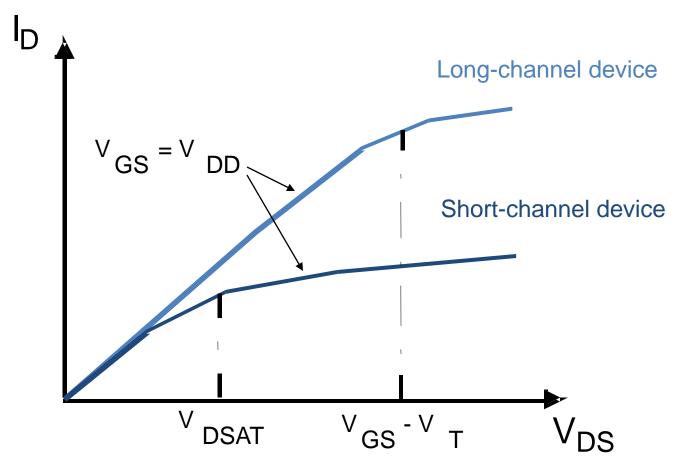

## 2<sup>nd</sup>-order effects affecting transistor operation

Subthreshold leakage current (when Vgs < Vt)

Velocity saturation

Parasitic resistances

Junction leakage current

# Perspective

When increasing the VDS, the electrical field in the channel ultimately reaches the critical value and the carriers at the drain become velocity saturated (gives a early saturation at VDSAT).

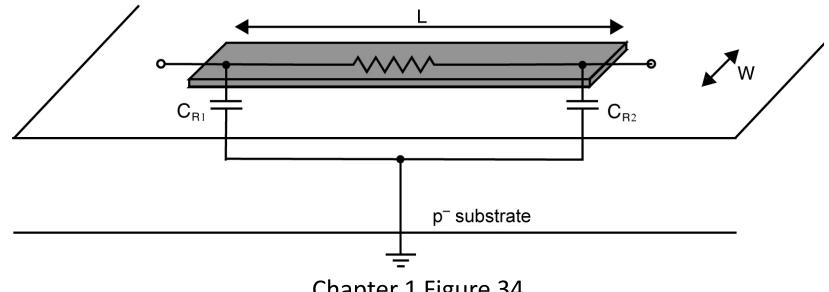

## **Resistor in an IC**

Chapter 1 Figure 34

The simplest realization of an integrated circuit resistor is a strip of conductive material above the silicon substrate.

The conductivity of the material is characterized by sheet resistance,  $R_{\Box}$

$$\mathbf{R} = \mathbf{R}_{\Box} \left( \frac{\mathbf{L}}{\mathbf{W}} \right)$$

It has parasitic capacitance in the model.

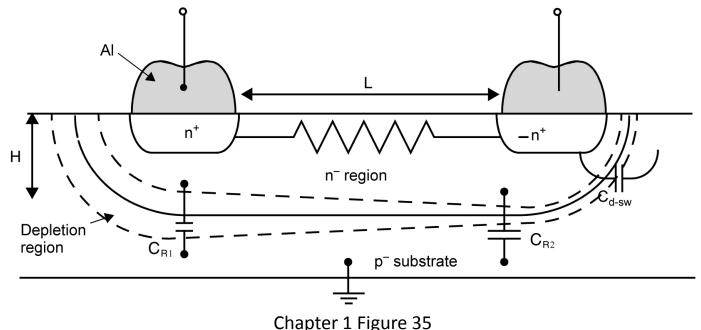

## Resistor in an IC

A lightly-doped nwell with contacts at both ends may be used a resistor.

The model still apply for this type of resistor. However, it has complex dependency on temperature and the voltage across it, making it varying and nonlinear.

Another method to implement a resistor is to operate a transistor in triode region, where the resistance is mostly modulated by Vgs.

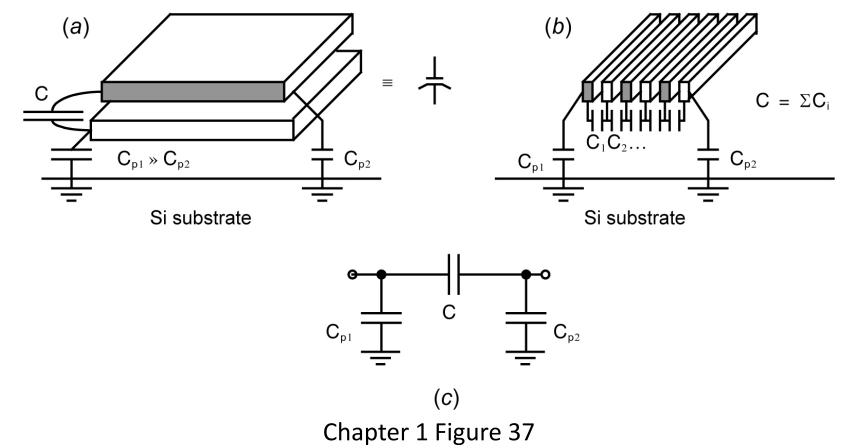

## Capacitor in an IC

For implementation of a linear capacitor, metal-to-metal is a popular approach.

$C \cong \frac{\varepsilon_{ox}A}{t_{ox}}$

where  $t_{ox}$  is the spacing between plates (on the order of 0.1 - 10  $\mu$ m),  $\epsilon_{ox}$  is the permittivity of the insulator between plates (often silicon dioxide, for which  $\epsilon_{ox} \approx 3.9\epsilon_0$ ), and A is the area of the plate.

Other approaches, such as poly-to-poly, poly-to-diffusion, are possible.

#### **SPICE model parameters**

| SPICE<br>Parameter | Model<br>Constant  | <b>Brief Description</b>           | Typical Value         |  |  |

|--------------------|--------------------|------------------------------------|-----------------------|--|--|

| IS                 | Is                 | Transport saturation current       | $10^{-17} \mathrm{A}$ |  |  |

| RS                 | R <sub>d</sub>     | Series resistance                  | 30 Ω                  |  |  |

| TT                 | $	au_{\mathrm{T}}$ | Diode transit time                 | 12 ps                 |  |  |

| CJ                 | $C_{j0}$           | Capacitance at 0-V bias            | 0.01 pF               |  |  |

| MJ                 | m <sub>j</sub>     | Diode grading coefficient exponent | 0.5                   |  |  |

| PB                 | $\Phi_0$           | Built-in diode contact potential   | 0.9 V                 |  |  |

| Chapter 1 Table 02 |                    |                                    |                       |  |  |

#### Table 1.2 Important SPICE parameters for modelling diodes.

| SPICE<br>Parameter | Model<br>Constant   | <b>Brief Description</b>                                          | Typical Value                                       |  |

|--------------------|---------------------|-------------------------------------------------------------------|-----------------------------------------------------|--|

| VTO                | $V_{tn}$ : $V_{tp}$ | Transistor threshold voltage (in V)                               | 0.8:-0.9                                            |  |

| UO                 | $\mu_n:\mu_p$       | Carrier mobility in bulk (in cm <sup>2</sup> /V·s)                | 500:175                                             |  |

| TOX                | t <sub>ox</sub>     | Thickness of gate oxide (in m)                                    | $1.8	imes 10^{-8}$                                  |  |

| LD                 | L <sub>D</sub>      | Lateral diffusion of junction under gate (in m)                   | $6	imes 10^{-8}$                                    |  |

| GAMMA              | γ                   | Body-effect parameter                                             | 0.5: 0.8                                            |  |

| NSUB               | $N_A:N_D$           | The substrate doping (in cm <sup>-3</sup> )                       | $3 \times 10^{16}$ : $7.5 \times 10^{16}$           |  |

| PHI                | $ 2\phi_F $         | Surface inversion potential (in V)                                | 0.7                                                 |  |

| PB                 | $\Phi_0$            | Built-in contact potential of junction to bulk (in V)             | 0.9                                                 |  |

| CJ                 | $C_{j0}$            | Junction-depletion capacitance at 0-V bias (in F/m <sup>2</sup> ) | $2.5 	imes 10^{-4}$ : $4.0 	imes 10^{-4}$           |  |

| CJSW               | $C_{j-sw0}$         | Sidewall capacitance at 0-V bias (in F/m)                         | $2.0 	imes 10^{^{-10}}  m{:} 2.8 	imes 10^{^{-10}}$ |  |

| MJ                 | m <sub>j</sub>      | Bulk-to-junction exponent (grading coefficient)                   | 0.5                                                 |  |

| MJSW               | m <sub>j-sw</sub>   | Sidewall-to-junction exponent (grading coefficient)               | 0.3                                                 |  |

**Table 1.3** A reasonable set of Level 2 or 3 MOS parameters for a typical 0.8- $\mu$ m technology.

| SPICE<br>Model | Main strengths compared with previous device models                                                                                                                                                                                                                                                |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BSIM3          | Improved modeling of moderate inversion, and the geometry-dependence of device parameters. This also marked a return to a more physics-based model as opposed to the preceding highly empirical models.                                                                                            |

| EKV            | Relates terminal currents and voltages with unified equations that cover all modes of transistor operation, hence avoiding discontinuities at transitions between, for example, weak and strong inversion. Also handles geometry-dependent device parameters.                                      |

| BSIM4          | Improved modeling of leakage currents and short-channel effects, noise, and parasitic resistance<br>in the MOSFET terminals, as well as continued improvements in capturing the geometry-<br>dependence of device parameters.                                                                      |

| PSP            | Improved modeling of noise and the many short-channel and layout-dependent effects now dominant in nanoscale CMOS devices. Particular effort was made to accurately model nonlinearities, which requires accuracy in the high-order derivatives of the transistor's voltage–current relationships. |

#### Table 1.4 A summary of modern SPICE model formats.

|                                           | 0.8  | μ <b>m</b> | 0.35 | 5 μ <b>m</b> | 0.18 | <b>β μm</b> | 45   | nm    |

|-------------------------------------------|------|------------|------|--------------|------|-------------|------|-------|

| Technology                                | NMOS | PMOS       | NMOS | PMOS         | NMOS | PMOS        | NMOS | PMOS  |

| $\mu C_{ox} \ (\mu A/V^2)$                | 92   | 30         | 190  | 55           | 270  | 70          | 280  | 70    |

| $V_{t0}$ (V)                              | 0.80 | -0.90      | 0.57 | -0.71        | 0.45 | -0.45       | 0.45 | -0.45 |

| $\lambda \cdot L$ (µm/V)                  | 0.12 | 0.08       | 0.16 | 0.16         | 0.08 | 0.08        | 0.10 | 0.15  |

| $C_{ox}$ (fF/ $\mu$ m <sup>2</sup> )      | 1.8  | 1.8        | 4.5  | 4.5          | 8.5  | 8.5         | 25   | 25    |

| t <sub>ox</sub> (nm)                      | 18   | 18         | 8    | 8            | 5    | 5           | 1.2  | 1.2   |

| n                                         | 1.5  | 1.5        | 1.8  | 1.7          | 1.6  | 1.7         | 1.85 | 1.85  |

| θ (1/V)                                   | 0.06 | 0.135      | 1.5  | 1.0          | 1.7  | 1.0         | 2.3  | 2.0   |

| m                                         | 1.0  | 1.0        | 1.8  | 1.8          | 1.6  | 2.4         | 3.0  | 3.0   |

| $C_{ov}/W = L_{ov}C_{ox}$<br>(fF/µm)      | 0.20 | 0.20       | 0.20 | 0.20         | 0.35 | 0.35        | 0.50 | 0.50  |

| $C_{db}/W \approx C_{sb}/W$ (fF/ $\mu$ m) | 0.50 | 0.80       | 0.75 | 1.10         | 0.50 | 0.55        | 0.45 | 0.50  |

Table 1.5MOSFET parameters representative of various CMOS technologies and used for<br/>rough hand calculations in this text.

#### **Summary**

| $g_m = \mu_n C_{ox} \left( \frac{W}{L} \right) V_{eff}$                                         | $g_{m} = \sqrt{2\mu_{n}C_{ox}(W/L)I_{D}}$                                     |                                           |  |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------|--|

| $g_m = \frac{2I_D}{V_{eff}}$                                                                    | $\mathbf{g}_{s} = \frac{\gamma \mathbf{g}_{m}}{2\sqrt{V_{SB} +  2\phi_{F} }}$ |                                           |  |

| $\mathbf{r}_{ds} = \frac{1}{\lambda \mathbf{I}_{D-sat}} \cong \frac{1}{\lambda \mathbf{I}_{D}}$ | $g_s \cong 0.2g_m$                                                            |                                           |  |

| $\lambda = \frac{k_{rds}}{2L\sqrt{V_{DS} - V_{eff} + \Phi_0}}$                                  | $k_{rds} = \sqrt{\frac{2K_s\varepsilon_0}{qN_A}}$                             | $C_{sb} = (A_s + WL)C_{js} + P_sC_{j-sw}$ |  |

| $C_{gs} = \frac{2}{3}WLC_{ox} + WL_{ov}C_{ox}$                                                  | $C_{gd} = WL_{ov}C_{ox}$                                                      | $C_{db} = A_d C_{jd} + P_d C_{j-sw}$      |  |

$\mathbf{C}_{js} = \frac{\mathbf{C}_{j0}}{\sqrt{1 + \mathbf{V}_{SB}/\Phi_0}}$

$\mathbf{C}_{jd} = \frac{\mathbf{C}_{j0}}{\sqrt{1 + \mathbf{V}_{DB} / \Phi_0}}$