# LM3046 Transistor Array General Description

The LM3046 consists of five general purpose silicon NPN transistors on a common monolithic substrate. Two of the transistors are internally connected to form a differentially-connected pair. The transistors are well suited to a wide variety of applications in low power system in the DC through VHF range. They may be used as discrete transistors in conventional circuits however, in addition, they provide the very significant inherent integrated circuit advantages of close electrical and thermal matching. The LM3046 is supplied in a 14-lead molded small outline package.

#### **Features**

- Two matched pairs of transistors V<sub>BE</sub> matched ±5 mV Input offset current 2 µA max at I<sub>C</sub> = 1 mA

- Five general purpose monolithic transistors

- Operation from DC to 120 MHz

- Wide operating current range

- Low noise figure: 3.2 dB typ at 1 kHz

### **Applications**

- General use in all types of signal processing systems operating anywhere in the frequency range from DC to VHF

- Custom designed differential amplifiers

- Temperature compensated amplifiers

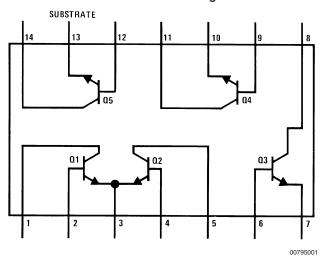

## **Schematic and Connection Diagram**

#### **Small Outline Package**

Top View Order Number LM3046M See NS Package Number M14A

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/

Distributors for availability and specifications. (T  $_{\!A}=25\,^{\circ}\text{C})$

|                                                           | LM30           |         |       |

|-----------------------------------------------------------|----------------|---------|-------|

|                                                           | Each           | Total   | Units |

|                                                           | Transistor     | Package |       |

| Power Dissipation:                                        |                |         |       |

| $T_A = 25^{\circ}C$                                       | 300            | 750     | mW    |

| $T_A = 25^{\circ}C$ to $55^{\circ}C$                      | 300            | 750     | mW    |

| $T_A > 55^{\circ}C$                                       | Derate at 6.67 |         | mW/°C |

| $T_A = 25^{\circ}C$ to $75^{\circ}C$                      |                |         | mW    |

| $T_A > 75^{\circ}C$                                       |                |         | mW/°C |

| Collector to Emitter Voltage, $V_{CEO}$                   | 15             |         | V     |

| Collector to Base Voltage, V <sub>CBO</sub>               | 20             |         | V     |

| Collector to Substrate Voltage, V <sub>CIO</sub> (Note 2) | 20             |         | V     |

| Emitter to Base Voltage, $V_{\text{EBO}}$                 | 5              |         | V     |

| Collector Current, I <sub>C</sub>                         | 50             |         | mA    |

| Operating Temperature Range                               | −40°C to       | +85°C   |       |

| Storage Temperature Range                                 | −65°C to       | +85°C   |       |

| Soldering Information                                     |                |         |       |

| Dual-In-Line Package Soldering (10 Sec.)                  | 260°C          |         |       |

215°C

220°C

See AN-450 "Surface Mounting Methods and Their Effect on Product Reliability" for other methods of soldering surface mount devices.

Infrared (15 Seconds)

Small Outline Package Vapor Phase (60 Seconds)

## **Electrical Characteristics**

$(T_A = 25^{\circ}C \text{ unless otherwise specified})$

| B                                                              | Conditions                                        |     | Limits |     |       |

|----------------------------------------------------------------|---------------------------------------------------|-----|--------|-----|-------|

| Parameter                                                      | Conditions                                        | Min | Тур    | Max | Units |

| Collector to Base Breakdown Voltage (V <sub>(BR)CBO</sub> )    | $I_{\rm C} = 10 \ \mu {\rm A}, \ I_{\rm E} = 0$   | 20  | 60     |     | V     |

| Collector to Emitter Breakdown Voltage (V <sub>(BR)CEO</sub> ) | $I_{\rm C} = 1 \text{ mA}, I_{\rm B} = 0$         | 15  | 24     |     | V     |

| Collector to Substrate Breakdown                               | $I_{\rm C} = 10 \ \mu \text{A}, \ I_{\rm CI} = 0$ | 20  | 60     |     | V     |

| Voltage (V <sub>(BR)CIO</sub> )                                |                                                   |     |        |     |       |

| Emitter to Base Breakdown Voltage (V <sub>(BR)EBO</sub> )      | I <sub>E</sub> 10 μA, I <sub>C</sub> = 0          | 5   | 7      |     | V     |

| Collector Cutoff Current (I <sub>CBO</sub> )                   | $V_{CB} = 10V, I_{E} = 0$                         |     | 0.002  | 40  | nA    |

| Collector Cutoff Current (I <sub>CEO</sub> )                   | V <sub>CE</sub> = 10V, I <sub>B</sub> = 0         |     |        | 0.5 | μΑ    |

| Static Forward Current Transfer                                | $V_{CE} = 3V$ $I_{C} = 10 \text{ mA}$             |     | 100    |     |       |

| Ratio (Static Beta) (h <sub>FE</sub> )                         | $I_C = 1 \text{ mA}$                              | 40  | 100    |     |       |

|                                                                | $I_C = 10 \mu A$                                  |     | 54     |     |       |

| Input Offset Current for Matched                               | $V_{CE} = 3V$ , $I_{C} = 1$ mA                    |     | 0.3    | 2   | μΑ    |

| Pair $Q_1$ and $Q_2  I_{O1} - I_{IO2} $                        |                                                   |     |        |     |       |

| Base to Emitter Voltage (V <sub>BE</sub> )                     | $V_{CE} = 3V$ $I_{E} = 1 \text{ mA}$              |     | 0.715  |     | V     |

|                                                                | $I_E = 10 \text{ mA}$                             |     | 0.800  |     |       |

| Magnitude of Input Offset Voltage for                          | $V_{CE} = 3V$ , $I_{C} = 1$ mA                    |     | 0.45   | 5   | mV    |

| Differential Pair IV <sub>BE1</sub> – V <sub>BE2</sub> I       |                                                   |     |        |     |       |

| Magnitude of Input Offset Voltage for Isolated                 | $V_{CE} = 3V$ , $I_{C} = 1$ mA                    |     | 0.45   | 5   | mV    |

| Transistors $ V_{BE3} - V_{BE4} $ , $ V_{BE4} - V_{BE5} $ ,    |                                                   |     |        |     |       |

| $ V_{BE5} - V_{BE3} $                                          |                                                   |     |        |     |       |

## **Electrical Characteristics** (Continued)

$(T_A = 25^{\circ}C \text{ unless otherwise specified})$

| Parameter                                                       | Conditions                                    | Limits |      |     | Units |

|-----------------------------------------------------------------|-----------------------------------------------|--------|------|-----|-------|

|                                                                 |                                               | Min    | Тур  | Max | Units |

| Temperature Coefficient of Base to                              | $V_{CE} = 3V$ , $I_{C} = 1$ mA                |        | -1.9 |     | mV/°C |

| Emitter Voltage                                                 |                                               |        |      |     |       |

| $\left( rac{\Delta V_{BE}}{\Delta T} \right)$                  |                                               |        |      |     |       |

| Collector to Emitter Saturation Voltage (V <sub>CE(SAT)</sub> ) | I <sub>B</sub> = 1 mA, I <sub>C</sub> = 10 mA |        | 0.23 |     | V     |

| Temperature Coefficient of                                      | $V_{CE} = 3V$ , $I_{C} = 1$ mA                |        | 1.1  |     | μV/°C |

| Input Offset Voltage                                            |                                               |        |      |     |       |

| $\left(\frac{\Delta V_{10}}{\Delta T}\right)$                   |                                               |        |      |     |       |

**Note 1:** "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits.

**Note 2:** The collector of each transistor is isolated from the substrate by an integral diode. The substrate (terminal 13) must be connected to the most negative point in the external circuit to maintain isolation between transistors and to provide for normal transistor action.

## **Electrical Characteristics**

| Parameter                                                      | Conditions                             | Min | Тур                    | Max | Units |  |

|----------------------------------------------------------------|----------------------------------------|-----|------------------------|-----|-------|--|

| Low Frequency Noise Figure (NF)                                | $f = 1 \text{ kHz}, V_{CE} = 3V,$      |     | 3.25                   |     | dB    |  |

|                                                                | $I_C$ = 100 μA, $R_S$ = 1 k $\Omega$   |     |                        |     |       |  |

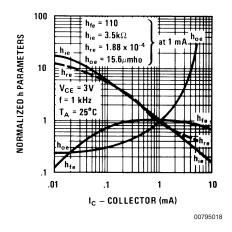

| LOW FREQUENCY, SMALL SIGNAL EQUIVALENT CIRCUIT CHARACTERISTICS |                                        |     |                        |     |       |  |

| Forward Current Transfer Ratio (h <sub>fe</sub> )              | $f = 1 \text{ kHz}, V_{CE} = 3V,$      |     | 110                    |     |       |  |

|                                                                | I <sub>C</sub> = 1 mA                  |     |                        |     |       |  |

| Short Circuit Input Impednace (hie)                            |                                        |     | 3.5                    |     | kΩ    |  |

| Open Circuit Output Impedance (hoe)                            |                                        |     | 15.6                   |     | μmho  |  |

| Open Circuit Reverse Voltage Transfer Ratio (hre)              |                                        |     | 1.8 x 10 <sup>-4</sup> |     |       |  |

| ADMITTANCE CHARACTERISTICS                                     |                                        |     |                        |     |       |  |

| Forward Transfer Admittance (Y <sub>fe</sub> )                 | $f = 1 \text{ MHz}, V_{CE} = 3V,$      |     | 31 – j 1.5             |     |       |  |

| Input Admittance (Yie)                                         | I <sub>C</sub> = 1 mA                  |     | 0.3+J 0.04             |     |       |  |

| Output Admittance (Y <sub>oe</sub> )                           |                                        |     | 0.001+j 0.03           |     |       |  |

| Reverse Transfer Admittance (Y <sub>re</sub> )                 |                                        |     | See Curve              |     |       |  |

| Gain Bandwidth Product (f <sub>T</sub> )                       | $V_{CE} = 3V$ , $I_{C} = 3 \text{ mA}$ | 300 | 550                    |     |       |  |

| Emitter to Base Capacitance (C <sub>EB</sub> )                 | $V_{EB} = 3V, I_{E} = 0$               |     | 0.6                    |     | pF    |  |

| Collector to Base Capacitance (C <sub>CB</sub> )               | $V_{CB} = 3V, I_{C} = 0$               |     | 0.58                   |     | pF    |  |

| Collector to Substrate Capacitance (C <sub>CI</sub> )          | $V_{CS} = 3V, I_{C} = 0$               |     | 2.8                    |     | pF    |  |

## **Typical Performance Characteristics**

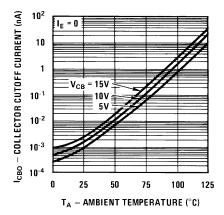

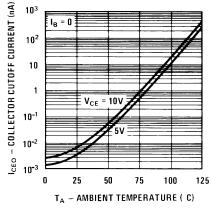

Typical Collector To Base Cutoff Current vs Ambient Temperature for Each Transistor

00795008

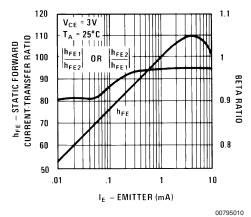

Typical Static Forward Current-Transfer Ratio and Beta Ratio for Transistors  $\mathbf{Q}_1$  and  $\mathbf{Q}_2$  vs Emitter Current

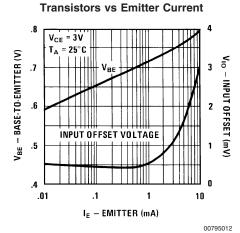

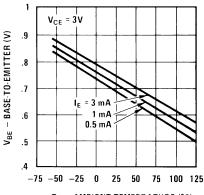

Typical Static Base To Emitter Voltage Characteristic and Input Offset Voltage for Differential Pair and Paired Isolated

Typical Collector To Emitter Cutoff Current vs Ambient Temperature for Each Transistor

00795009

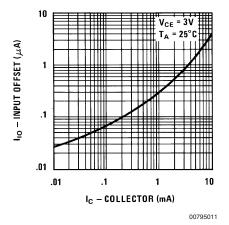

Typical Input Offset Current for Matched Transistor Pair Q<sub>1</sub> Q<sub>2</sub> vs Collector Current

Typical Base To Emitter Voltage Characteristic for

Voltage Characteristic for Each Transistor vs Ambient Temperature

TA - AMBIENT TEMPERATURE (°C)

00795013

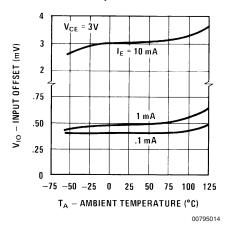

## Typical Performance Characteristics (Continued)

Typical Input Offset Voltage **Characteristics for Differential** Pair and Paired Isolated **Transistors vs Ambient** Temperature

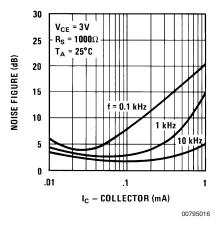

#### Typical Noise Figure vs **Collector Current**

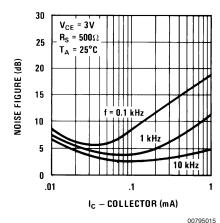

#### Typical Noise Figure vs **Collector Current**

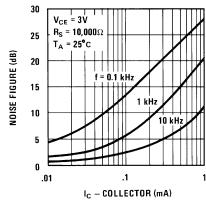

#### Typical Noise Figure vs **Collector Current**

00795017

www.national.com

## Typical Performance Characteristics (Continued)

Typical Normalized Forward

Current Transfer Ratio, Short

Circuit Input Impedance,

Open Circuit Output Impedance,

and Open Circuit Reverse

Voltage Transfer Ratio vs

Collector Current

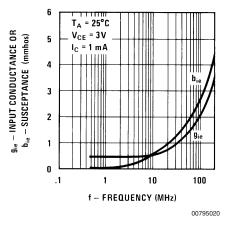

Typical Input Admittance vs Frequency

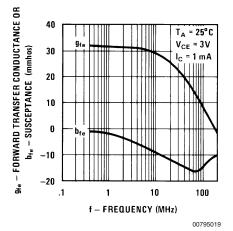

Typical Reverse Transfer Admittance vs Frequency

**Typical Forward Transfer Admittance vs Frequency**

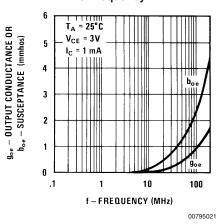

## Typical Output Admittance vs Frequency

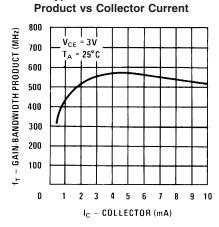

Typical Gain-Bandwidth

00795023

www.national.com

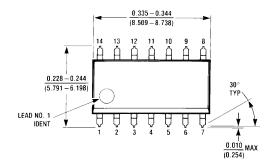

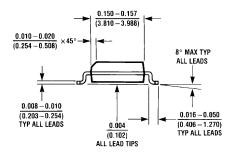

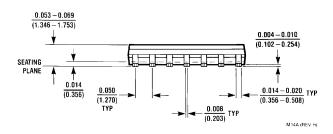

### Physical Dimensions inches (millimeters)

unless otherwise noted

Molded Small Outline Package (M) Order Number LM3046M NS Package Number M14A

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor

Europe Customer Support Center

Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.con

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560